近日,日本东京大学与北陆先端科学技术大学院大学(JAIST)研发出一种通过“原子层堆积法(ALD法)”而非传统的溅射法来进行氧化物半导体-氧化铟(In2O3)镀膜的技术,并成功开发出了三维通道型铁电体及反铁电体晶体管存储器。

该成果是东京大学生产技术研究所的小林正治副教授和JAIST先端科学技术研究科的浦冈行治教授组成的联合研究团队取得的,并于美国夏威夷州当地时间6月11日~12日举行的2022 IEEE Symposium on VLSI Technology and Circuits的专题研讨会IEEE Silicon Nanoelectronics Workshop 2022上发表。(详见:https://snw2022.conf.nycu.edu.tw/ )

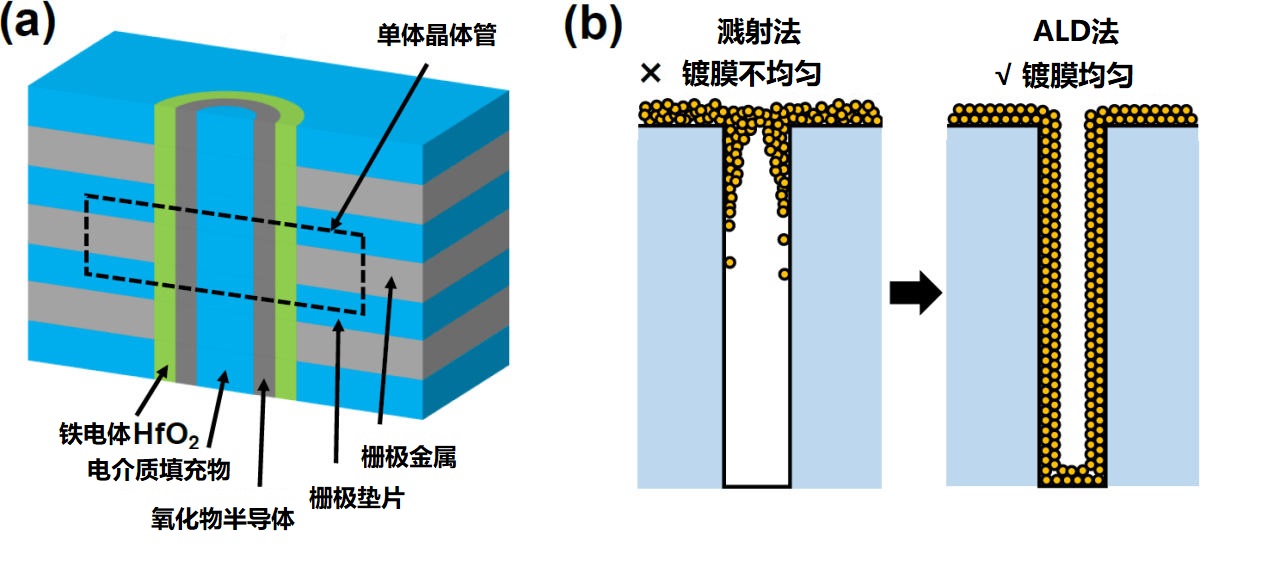

大容量记忆存储通常是用NAND(计算机存储设备),但由于其耗电量大所以普遍认为不适合用于物联网设备(IoT)。铁电体晶体管(FeFET)存储器由于其铁电体性质耗电量小,但此前人们并不知道它可以实现NAND那样高密度的三维垂直通道结构。特别是3D NAND这样的通道如果使用多晶硅的话,由于多晶硅的低迁移率导致读取速度缓慢、铁电体和多晶硅之间会形成低介电常数层而导致电荷捕获的可靠性降低和写入电压无法降低等问题就会出现。为了解决这些问题,研究团队试着用IGZO等氧化物半导体为渠道的FeFET存储器,发现理论上是有可能实现的。不过,要想对氧化物半导体进行三维结构的镀膜,以往的溅射法的话镀膜的沉积性难度非常高,为了实现ALD法研究团队开发了用In2O3进行镀膜的技术。用ALD法实际做出了将In2O3进行三维结构的均匀镀膜,所做出的薄膜晶体管的迁移率超过了40cm2/Vs。

此外,团队还使用ALD法试制了以二氧化锆(HfZrO2)铁电体为栅极绝缘体的FeFET存储器,如理论预期,1.5V的存储窗口(阈值电压差)、超过1万次的读写耐性、保持特性超过1000秒。

配图:(a)将氧化物半导体通道化的三维垂直通道型FeFET的模式图。栅极绝缘体使用的是铁电体HfO2。

(b)将氧化物半导体进行三维结构镀膜的问题及解决方法。通过使用ALD法,实现三维结构的均匀镀膜。

出处:发布会PDF

该研究团队还有一个方案,将二氧化锆(ZrO2)作为绝缘膜的“反铁电体晶体管”(AFeFET)。氧化物半导体是N型半导体,虽然容易吸引大多数载体的电子,但是少数载体的正孔却很难。于是根据程序状态下删除状态的保留特性容易退化这一特征,通过使用反铁电体,即便是不吸引少数载体电子也可以进行删除动作,得以改善删除状态的保留特性。

配图:(a)试制的三维垂直通道型FeFET的切面透视式电子显微镜图像。铁电体HfO2和氧化物半导体In2O3一起均匀镀膜。

(b)试制的原型装置的整体截面模拟图。

出处:发布会PDF

通过该研究的实际论证,这一技术的高密度和低电耗特性使其可以应用于物联网(IoT)设备的记忆存储器上,需要广泛使用大数据的社会服务项目就指日可待了。

Copyright © 2003-2036 北京三吉世纪科技有限公司Beijing CYCAD Century Science and Technology Co.,Ltd.版权所有 京ICP备14025030号-1 北京市开发区分局11030102011349